# 300mA LDO Linear Regulator with Integrated Reset Circuit

### DESCRIPTION

The MP6401 combines a low-dro pout linear regulator with an integrated reset circuit. It operates from a 2.5V to 5.5V input voltage and regulates the output voltage with 2% accuracy at 1.8V, 2.5V, 3.3V or adjustable value. It delivers up to 300mA of load current. By combining an LDO linear regulator with a reset circuit, these products can reduce cost and save space in compact portable devices such as cell phones, smart phones, PDAs, PMPs, and portable GPS devices.

The MP640 1 provides a push-pull, active-low that asserts when the regulator out put voltage drops below the microprocessor supply threshold (-7.5% or -12.5% of no minal output voltage). Four reset delay time, 3.125ms, 25ms, 200ms and 1580ms can be selected. The MP6401 is available in 3mmx3 mm T QFN8, 2mmx2mm TQFN6 and TSOT packages and is specified for operation from -40°C to 85°C.

#### **FEATURES**

- Low Quiescent Current of 80 µA for Battery Powered Equipment

- Low 114mV Dropout at 300mA Output

- ±2 % Accurate Output Voltage

- Fixed Output Voltage Options of 1. 8V, 2.5V or 3.3V

- Adjustable Output Voltage from 1. 229V to 5V Using an External Resistor Divider

- 15 μV<sub>RMS</sub> Ultra Low Noise Output

- PSRR: 57dB at 1kHz

- Input Reverse Current, Thermal and Short-Circuit Protection

- Microprocessor Reset with Four Delay time Options

- Push-Pull RESET

#### **APPLICATIONS**

- Smart Phone and Cell Phone

- Portable GPS Devices

- Wireless Devices

- PDA and PMP

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website un der Q uality Assurance. "MPS" and "The Future of An alog IC Technology" are Re gistered T rademarks of Mo nolithic Power Systems, Inc.

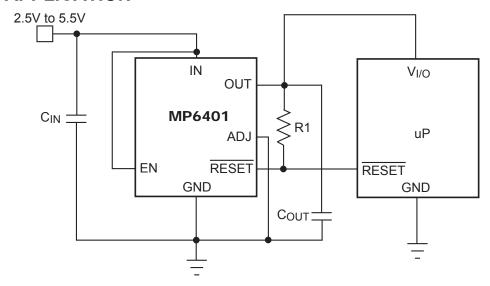

### TYPICAL APPLICATION

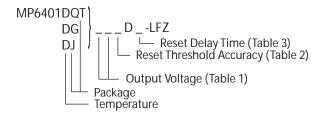

# **ORDERING INFORMATION**

| Part Number*    | Package         | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|-----------------|-----------------|-------------|----------------------------------------|

| MP6401DQT-18AD3 |                 | 7T          |                                        |

| MP6401DQT-18BD3 |                 | 8T          |                                        |

| MP6401DQT-25AD3 | TQFN8 (3mmx3mm) | 5T          |                                        |

| MP6401DQT-25BD3 |                 | 6T          |                                        |

| MP6401DQT-33BD3 |                 | 4T          |                                        |

| MP6401DGT-18AD3 |                 | 7T          |                                        |

| MP6401DGT-18BD3 |                 | 8T          |                                        |

| MP6401DGT-25AD3 | TQFN6 (2mmx2mm) | 5T          | –40°C to +85°C                         |

| MP6401DGT-25BD3 |                 | 6T          |                                        |

| MP6401DGT-33BD3 |                 | 4T          |                                        |

| MP6401DJ-18AD3  |                 | 7T          |                                        |

| MP6401DJ-18BD3  |                 | 8T          |                                        |

| MP6401DJ-25AD3  | TSOT23-6        | 5T          |                                        |

| MP6401DJ-25BD3  |                 | 6T          |                                        |

| MP6401DJ-33BD3  |                 | 4T          |                                        |

<sup>\*</sup> For other versions, contact factory for availability.

#### Note:

Table 1—Output Voltage Suffix Guide

| Suffix Ou | tpu | t Voltage |

|-----------|-----|-----------|

| 18        |     | 1.8       |

| 25        |     | 2.5       |

| 33        |     | 3.3       |

**Table 2—Reset Threshold Accuracy**

| Suffix | Suffix Vout Reset Threshold (%) |  |  |  |

|--------|---------------------------------|--|--|--|

| Α      | -7.5%                           |  |  |  |

| В      | -12.5%                          |  |  |  |

Table 3—Reset Delay Time Guide

| Suffix | Typical Reset Delay Time (ms) |

|--------|-------------------------------|

| D1     | 3.125                         |

| D2     | 25                            |

| D3     | 200                           |

| D4     | 1580                          |

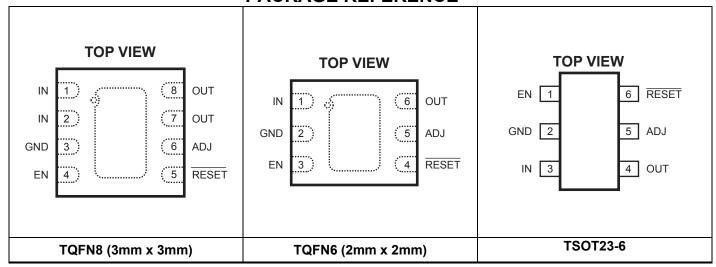

### PACKAGE REFERENCE

# **ABSOLUTE MAXIMUM RATINGS** (1)

| ADJ                   | 0.3V to + 6 V<br>0.3V to 6V<br>0.3V to 6V         |

|-----------------------|---------------------------------------------------|

| Continuous Power Diss | sipation. (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                       | 2.6W                                              |

|                       | 1.56W                                             |

|                       | 0.57W                                             |

| Junction Temperature. | 150°C                                             |

|                       | 260°C                                             |

| •                     | –65°C to +150°C                                   |

|                       | (3)                                               |

##

| Thermal Resistance TQFN8 (3mm x 3mm) | •,  |       | .°C/W |

|--------------------------------------|-----|-------|-------|

| TQFN6 (2mm x 2mm)                    | 80  | 16    | .°C/W |

| TSOT                                 | 220 | 110 . | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T J (MAX), the junction-to-ambient thermal r esistance θ<sub>JA</sub>, and t he ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated b y P<sub>D</sub> (MAX) = (T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause ex cessive die temperature, and the regulator will go into the rmal shutdown. Internal thermal shutdown circuitr y pr otects the device from permanent damage. Thermal shutdown e ngages at T<sub>J</sub>=150°C(TYP) and disengages at T<sub>J</sub>=130°C(TYP)

- The device is not guarant eed to function outside of its operating conditions.

- 4) Measured on JESD51-7 4-layer board.

# **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN}}$  = ( $V_{\text{OUT}}$  + 0.5V) or +2.5V, whichever is greater,  $C_{\text{OUT}}$  = 3.3 $\mu$ F. Typical Value at  $T_{\text{A}}$  = +25°C unless otherwise noted.

| Parameter Sy                                                        | mbol                  | Condition                                                                     | Min       | Тур     | Max                | Unit             |

|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------|-----------|---------|--------------------|------------------|

| Input Supply Range                                                  | $V_{IN}$              |                                                                               | 2.5       |         | 5.5                | V                |

| Input Undervoltage Lockout                                          | $V_{\text{UVLO}}$     | V <sub>IN</sub> falling 1.85                                                  |           | 2.05    | 2.2                | V                |

| Hysteresis of UVLO                                                  | $V_{HYS}$             |                                                                               |           | 190     | mV                 |                  |

| Supply Cu rrent (G round Current)                                   | $I_Q$                 | I <sub>OUT</sub> = 0                                                          |           | 80      | 155                | μΑ               |

| Shutdown Supply Current                                             | I <sub>SHDN</sub>     | T <sub>A</sub> =+25°C                                                         |           | 0.1     | 1                  | μΑ               |

| Regulation Circuit                                                  |                       |                                                                               |           |         |                    |                  |

| Output Current                                                      |                       |                                                                               | 300       |         |                    | mΑ               |

| Output Volt age A ccuracy (Fixed Output Voltage)                    |                       | 1mA ≤ I <sub>OUT</sub> ≤ 300mA                                                | -2        |         | +2                 | %                |

| Adjustable O utput Voltage Range                                    |                       |                                                                               | $V_{ADJ}$ |         | 5                  | V                |

| ADJ Reference Voltage                                               | $V_{ADJ}$             |                                                                               | 1.205     | 1.229   | 1.253              | V                |

| ADJ Threshold                                                       |                       |                                                                               |           | 250     |                    | mV               |

| ADJ Input Leakage Current                                           | $I_{ADJ}$             | $V_{ADJ} = 0, +1.2V$                                                          |           | ±20     | ±100               | nA               |

| Dropout Vo Itage (Fixe d Output Voltage) (5)                        | $\Delta V_{DO}$       | V <sub>OUT</sub> = +3.3V, I <sub>OUT</sub> = 300mA                            |           | 114     | 220                | mV               |

| Short Current Limit                                                 |                       | V <sub>IN</sub> ≥2.5V                                                         |           | 375     |                    | mA               |

| In Regulation Current Limit                                         |                       | V <sub>IN</sub> ≥2.5V                                                         |           | 500     |                    | mA               |

| Input Reve rse Lea kage<br>Current (O UT to I N<br>Leakage Current) |                       | $V_{IN} = 4V$ , $V_{OUT} = 5V$ , E N deasserted, $T_A = +25$ °C               | 0.01      |         | 1                  | μΑ               |

| EN Input Low Voltage                                                | V <sub>IL</sub>       |                                                                               |           |         | 0.3V <sub>IN</sub> | V                |

| EN Input High Voltage                                               | V <sub>IH</sub>       |                                                                               | 0.7Vin    |         | 010 1 IIV          | V                |

| EN Input Current                                                    |                       | EN= V <sub>IN</sub> or GND, T <sub>A</sub> =+25°C -1                          |           | 0.1     | +1                 | μA               |

| Thermal-Shutdown Temperature                                        | T <sub>SHDN</sub>     |                                                                               |           | 150     |                    | °C               |

| Thermal-Shutdown<br>Hysteresis                                      | $\Delta T_{\sf SHDN}$ |                                                                               | 20        |         |                    | °C               |

| Line Regulation                                                     |                       | $V_{OUT}$ =1.5V, 2.5V $\leq V_{IN} \leq 5.5V$ , $I_{OUT}$ = 10mA              | 0.02      |         |                    | %/V              |

| Load Regulation                                                     |                       | $V_{OUT} = 1.5V, V_{IN} = 2.5V,$<br>$1mA \le IOUT \le 150mA$                  | 0.1       |         |                    | %                |

| Output Voltage Noise                                                |                       | 10Hz to 100kHz, $C_{IN} = 0.1 \mu F$ , $I_{OUT} = 100 mA$ , $V_{OUT} = 1.5 V$ | 15        |         |                    | $\mu V_{RMS}$    |

| Reset Circuit                                                       |                       |                                                                               |           |         |                    |                  |

| V <sub>OUT</sub> Reset Threshold                                    | $V_{THOUT}$           | MP6401AD_                                                                     | 90        | 92.5    | 95                 | %                |

|                                                                     |                       | MP6401BD_                                                                     | 85        | 87.5    | 90                 | V <sub>OUT</sub> |

| V <sub>OUT</sub> to Reset Delay                                     |                       |                                                                               |           | 30      |                    | μs               |

|                                                                     |                       | D1                                                                            | 2.2       | 3.125   | 4.0                |                  |

|                                                                     |                       | D2                                                                            | 17.5      | 25      | 32.5               |                  |

| Reset Delay Time                                                    | $T_d$                 | D3 140                                                                        |           | 200     | 260                | ms               |

|                                                                     |                       | D4                                                                            | 1106 15   | 80 2054 |                    |                  |

|                                                                     |                       | = -                                                                           |           |         |                    |                  |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = ( $V_{OUT}$  + 0.5V) or +2.5V, whichever is greater,  $C_{OUT}$  = 3.3 $\mu$ F. Typical Value at  $T_A$  = +25°C unless otherwise noted.

| Parameter            | Symbol          | Condition                                                            | Min                 | Тур | Max | Unit |

|----------------------|-----------------|----------------------------------------------------------------------|---------------------|-----|-----|------|

| RESET Output Voltage | V <sub>OL</sub> | V <sub>OUT</sub> ≥ 1.0V, I <sub>SINK</sub> = 50μA,<br>RESET asserted |                     |     | 0.3 |      |

|                      |                 | $V_{OUT} \ge 1.5V$ , $I_{SINK} = 3.2mA$ , RESET asserted             |                     |     | 0.4 | V    |

|                      | $V_{OH}$        | $V_{OUT} \ge 2.0V$ , $I_{SOURCE} = 500\mu A$ , RESET deasse rted     | 0.8V <sub>OUT</sub> |     |     |      |

#### Notes:

<sup>5)</sup> Dropout Voltage is defined as the input to output differential when the output voltage drops 100mV below its nominal value.

# **PIN FUNCTIONS**

| TQFN8<br>Pin # | TQFN6<br>Pin# | TSOT<br>Pin# | Name  | Description                                                                                                                                                                                                  |

|----------------|---------------|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 1             | 3            | IN    | Supply input pin.                                                                                                                                                                                            |

| 2              |               | ,            |       |                                                                                                                                                                                                              |

| 3 2            |               | 2            | GND   | Ground.                                                                                                                                                                                                      |

| 4              | 3             | 1            | EN    | Enable (Active High). Connect EN to IN generally. Don't float EN pin.                                                                                                                                        |

| 5 4            |               | 6            | RESET | Push-pull RESET. It asserts when the OUT voltage drops below its threshold. When OUT voltage recover, RESET deasserts after a fix delay time (four options).                                                 |

| 6 5            |               | 5            | ADJ   | Mode selector input. When ADJ is connected to the tap of an external resistor divider from the OUT to GND, the OUT voltage is adjustable. When ADJ is connected to GND, a preset output voltage is selected. |

| 7              | 6             | 4            | OUT   | Regulator output pin.                                                                                                                                                                                        |

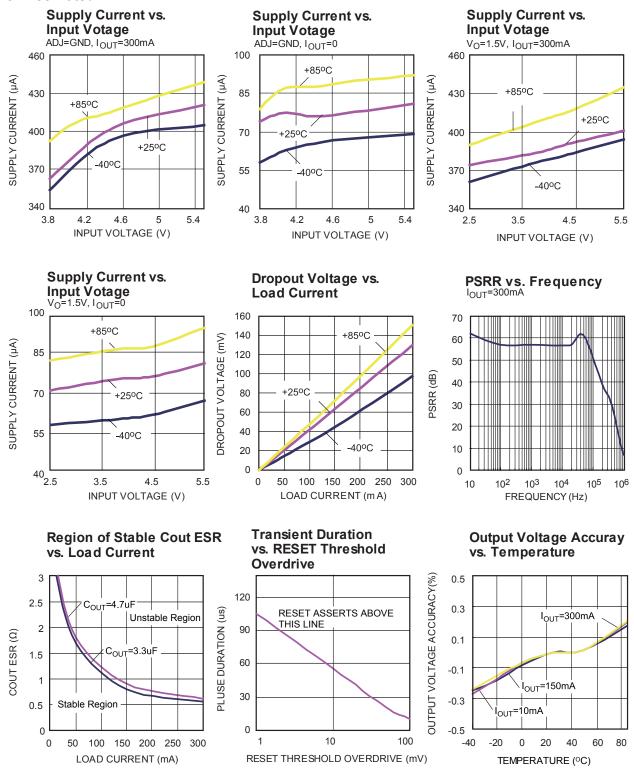

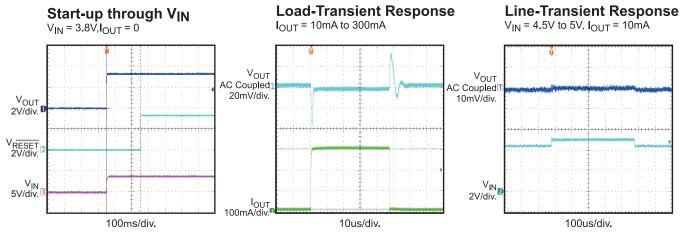

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{\text{IN}}$ =5V,  $V_{\text{OUT}}$ =3.3V,  $C_{\text{OUT}}$ =3.3 $\mu$ F,  $T_{\text{A}}$ = -40°C to +85°C, Typical values are at  $T_{\text{A}}$ =+25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$ =5V,  $V_{\text{OUT}}$ =3.3V,  $C_{\text{OUT}}$ =3.3 $\mu$ F,  $T_{\text{A}}$ = -40°C to +85°C, Typical values are at  $T_{\text{A}}$ =+25°C, unless otherwise noted.

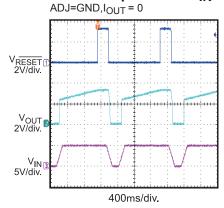

## Reset Response To VIN Rising

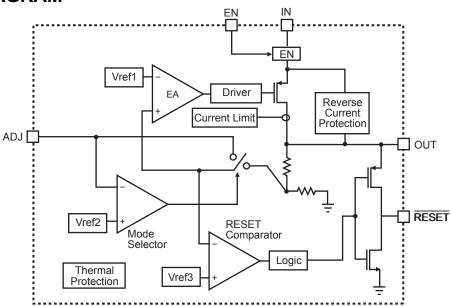

# **BLOCK DIAGRAM**

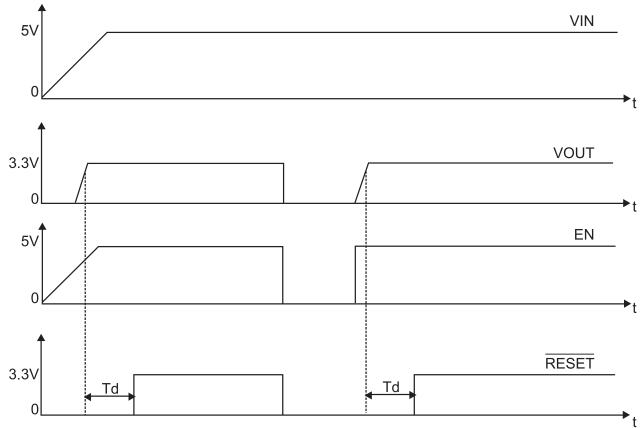

# **TIMING DIAGRAM**

Figure 2—RESET Timing Diagram

### **OPERATION**

The MP6401 integrates a low noise, low dropout, low quiescent current linear regulator and a microprocessor reset circuit. It operates from a 2.5V to 5.5V input voltage and regulates the fixed output voltage with 2% accuracy at 1.8V, 2.5V, 3.3V or adjustable value. The MP6401 can supply to 300mA of load current. The internal reset circuit is used to monitor the regulator output voltage. The RESET asserts when the re gulator output voltage drops below the standard microprocessor supply threshold.

### **Linear Regulator**

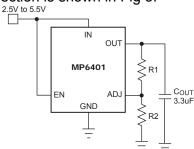

The MP6401 can output a fixed voltage (1.8V, 2.5V, 3.3V options) or adjustable voltage which ranges from 1.25V to 5V with 2.0% accuracy by operating from a +2.5V to +5.5V input. The MP6401 can supply up to 300mA of load current. When ADJ is connected to GND, a fixed output voltage is selected. Connecting ADJ pin to the tap of external resistor divider from the OUT to GND, adjustable output voltage is selected. The typical ADJ connection is shown in Fig 3.

Figure 3—Output Voltage Adjusted with Resistor Divider

#### **Reset Function**

The reset circuit monitors the OUT voltage. RESET asserts while OUT voltage falls below its threshold. Two OUT voltage thresholds (-7.5% and -12.5%) are available. The power-up, power-down, and brownout conditions will make RESET asserted. So MP640 1 monitor circuit could right control the microprocessor. RESET asserts when the input and output voltage below their thresholds. RESET asserts when EN is a low logic. When the assert trigger condition is removed, RESET will deassert after a fixed delay time. Four o ptions of reset delay-time (see Table 3) can be selected.

#### **EN Shutdown**

The MP6401 can be switched ON or OFF by a logic input at the EN pin. A high voltage at this pin will turn the device on. When the EN pin is low, the regulator output is off and the supply current is reduced. Generally, the EN pin should be tied to IN to keep the regulator output always on. Do not float the EN pin.

#### **Reverse Leakage Protection**

An internal circuit monitors  $V_{IN}$  and  $V_{OUT}$  to control the reverse leakage — current from OUT to IN. While  $V_{IN}$  decreases lower than  $V_{OUT}$  and EN s till hold logic h igh, the mo nitor circuit turns off the pass element and its parasitic diode. Typically the reverse leakage current through pass element decreases to 0.1uA.  $\overline{\text{RESET}}$  deasserts un til  $V_{IN}$  returns greater than  $V_{OUT}$  and  $V_{OUT}$  is higher than its preset threshold.

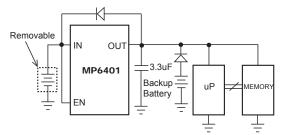

MP6401 also can work with backu p battery at OUT after input power supply is removed as shown in Fig 4. When input power supply is removed, RESET asserts. The backup battery will power the device through two external diodes and typically the current from OUT to ground is 40uA. So, the power supply removing does not erase RAM content if the voltage of backup battery is greater than memory's standby specification. The backup battery can be replaced by a super-cap, while the diode connected with battery is changed to a current-limiting resistor.

Figure 4— Maintain Memory with Backup Battery

#### **Current Limit**

The MP6401 includ es a current limit structur e which monit ors and controls pass element gate voltage limiting the guar anteed maximum output current to 500mA.

#### **Thermal Shutdown**

Thermal protection tur ns off the pass e lement when the junction temperature exceeds +150° C, allowing to cool the IC. When the IC's junction temperature drops by 20°C, the pass element will be turned on again. Thermal protection limits total power dissipation on the MP6401. For reliable operation, junction temperature should be limited to 125 °C maximum.

#### **APPLICATION INFORMATION**

### **Adjustable Regulator Output**

The OUT voltage of MP6401 has two modes available (fixed and ad justable out put voltage). When ADJ pin is connected to GND, the regulator works in fixed voltage mode. The regulator output voltage will equal to preset voltage (1.8V, 2.5V or 3.3V options). In fixed voltage mode, the impedance between ADJ and ground shou always be less than 5  $\,$  0k $\Omega$ . Generally, ADJ is connected directly to ground.

When the ADJ pin is connected to the tap of an external resistor divider, the regulator works in adjustable voltage mode as shown in Fig 3. The output voltage is selected by resistor divider, thus

$$V_{OUT} = 4.229 \frac{RR + \frac{2}{R_2}}{R_2}$$

In adjustable voltage mode, R  $_2$  equal to 13k  $\Omega$  is recommended as a good tradeoff among stability, accuracy a nd high-freq uency PSRR. R  $_2$  should be not greater than  $100k\Omega.$

#### **Power Dissipation**

The power dissipation for any package depend s on the thermal resistan ce of the ca se and circu it board, the temperature difference between the junction and ambient air, and the ra te of airflow. The power dissipat ion across the device can be represented by the equation:

$$P = (V_{IN} - V_{OUT}) \times I_{OUT}$$

The allowable power dissipation can be calculated using the following equation:

$$P_D(MAX) = (T_J(MAX)-T_A)/\theta_{JA}$$

Where  $(T_J(MAX)-T_A)$  is the temperature difference between the junctio  $\,$  n and the ambient environment,  $\theta_{JA}$  is the thermal re sistance from the junctio  $\,$  n to the ambient environment. Connecting the GND pi n of MP6401 to ground using a large pad or ground plane helps to channel heat away.

#### **Output Capacitor Selection**

The MP6401 is designed specifically to work with very low ESR ceramic output ca pacitor 3.3u F (min). For performance considera tion, a large ceramic capacitor such as 10uF is better. X7R or X5R capacitor dielectric is recommended.

#### **OUT Voltage Transient Immunity**

The MP640 1 can be immune to OUT pin short negative transient. Typically, the immune duration is 60us with 10mV overdriving. A shorter negative transient can not make the RESET output assert.

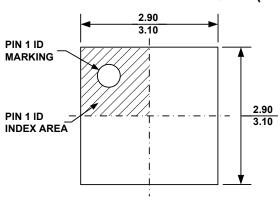

# **PACKAGE INFORMATION**

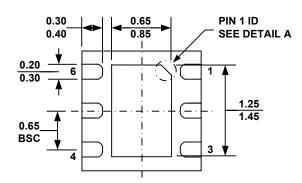

# TQFN8 (3mm x 3mm)

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

**DETAIL A**

**RECOMMENDED LAND PATTERN**

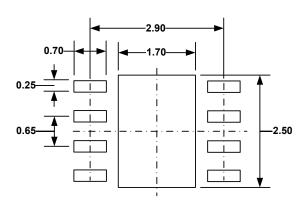

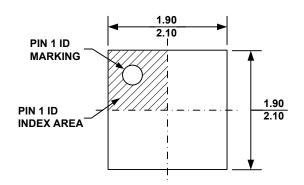

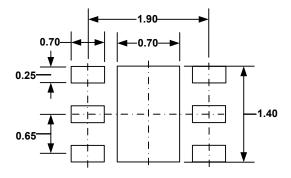

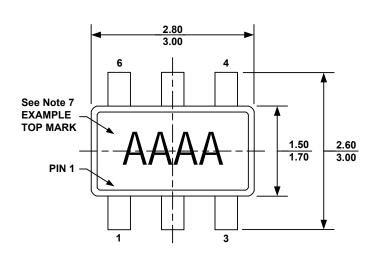

# TQFN6 (2mm x 2mm)

### **TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

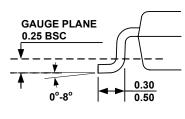

**DETAIL A**

#### **RECOMMENDED LAND PATTERN**

### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) JEDEC REFERENCE IS MO-229, VARIATION WCCC.

- 5) DRAWING IS NOT TO SCALE.

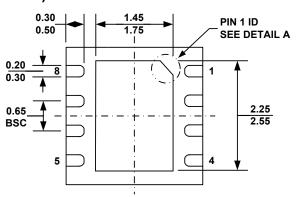

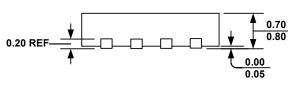

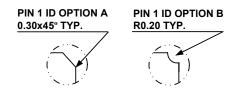

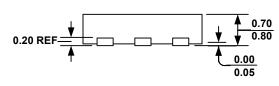

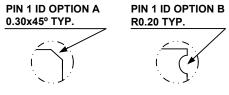

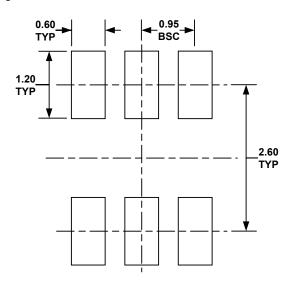

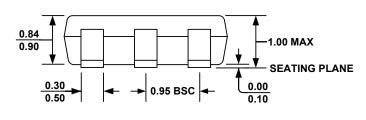

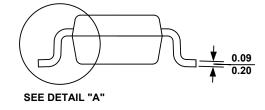

#### **TSOT23-6**

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

## NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-193, VARIATION AB.

- 6) DRAWING IS NOT TO SCALE.

- 7) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS product sinto any application. MPS will not assume any legal responsibility for any said applications.